# 擬似許容関数集合を用いたCMOS回路の消費電力の削減

世古 忠

Power Reduction for CMOS Circuits Using Sets of Pseudo Permissible Functions

#### Tadashi SEKO

This paper presents a new method to reduce the power consumption of CMOS circuits using the pseudo permissible functions. The new method extends the concept of a compatible set of permissible functions and it can indroduce much more circuits than the circuits generated by the previous methods. I define the measure  $\Phi$  of power of CMOS circuits and the transduction method based on the new pseudo permissible functions applies to the CMOS circuits to reduce the power consumption of CMOS circuits. The experimental evaluations using MCNC benchmark circuits show the superiority of the proposed approach.

#### 1. はじめに

近年,携帯用情報端末の発展に伴い,VLSIの設計において消費電力を削減することが重要な目標になっており,これまでに,VLSIを構成するCMOS論理回路の消費電力の削減手法がいくつか提案されてきた[1],[2],[3].

文献[1]の方法は局所的な回路変形を繰り返し消費電力を削減する手法であり、文献[2]はテスト生成で用いられる回路変形による消費電力削減手法である。更に、強力な回路最適化手法として知られるトランスダクション法[4]を消費電力削減に応用する研究[3]が行われてきた。トランスダクション法は両立許容関数集合 (CSPF: Compatible Sets of Permissible Functions) を用いて回路の局所的変換を行い回路を最適化する手法である。著者は、文献[6]で拡張CSPF[5]を用いた消費電力削減法を提案した。本論文ではCSPFより強力な回路変形能力をもつ擬似許容関数集合 $G_x$ を新しく提案し、これに基づいたCMOS回路の消費電力削減法を示す。

## 2. 消費電力のモデル

#### 2. 1 評価尺度Φ

CMOS論理回路の消費電力は式(1)で近似される.

$$P = 0.5 f V_d^2 \sum_{g \in M} (C_g T_g) \tag{1}$$

式(1)において、fはクロック周波数、 $V_d$ は電源電圧、Mは論理回路内のゲートの集合であり  $C_g$ 、 $T_g$ はそれぞれゲートの負荷容量、信号値遷移確率である。式(2)の  $C_g$ はゲートgのファンアウト数  $N_g$ に比例すると仮定し、本論文では消費電力の評価関数 $\Phi$ を次式で定義する。

$$\Phi = \sum_{g \in M} (N_g T_g) \tag{2}$$

ここで、ゲート

$$g$$

の出力が $1$ になる確率を $E$ とするとき、

$$T_g = E \cdot (1-E) \tag{3}$$

である。

### 3. 擬似許容関数集合

#### 3. 1 CSPF

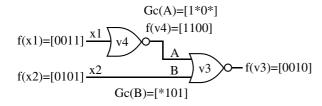

回路中の関数fをf'で置き換えても回路の出力が変わらないとき、f'を許容関数という。図1において真理値表をベクトルで表すとき、 $f(x_1)=[0011]$ 、 $f(x_2)=[0101]$ 、 $f(v_4)=[1100]$ 、 $f(v_3)=[0010]$ である。 $f(x_2)=[0101]$ を固定したとき、 $f(v_4)$ を[1000]で置き換えても、回路の出力 $f(v_3)$ は変化しないので、f' $(v_4)=[1000]$ は許容関数である。同様に $f(v_4)$ を[1001]、[1101]に置き換えても出力は変化しないので、[1001]、[1101]も許容関数である。このような結線Aの許容関数の集合を $G(A)=\{[1000]$ 、[1001]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100]、[1100] [1100]、[1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100] [1100]

(a) CSPF Gc(A), Gc(B)

(b) Gx(A), Gx(B)

図1 CSPFとGx

(A) = [1\*0\*], G(B) = [\*\*01]の2番目の要素は両方ともに\*であるが、両方ともに0にすると、出力が変化してしまうので、いずれか一方を1とし、他方は\*とした許容関数集合を考え、これを両立許容関数集合(CSPF:Compatible Sets of Permissible Functions)と呼び、 $G_c$ で表わす。例えば、図1において、 $G_c(A) = [1*0*]$ 、 $G_c(B) = [*101]$ である。

## 3. 2 疑似許容関数集合 $G_x$

両立許容関数集合を求めるとき図1(a)の例では,G(B)の2番目の要素を1とし,対応するG(A)の要素は\*としたが,G(A)の要素を1とし,G(B)の要素を\*とする可能性もある。本論文では,このような両方の可能性を考慮に入れた新しい疑似許容関数集合 $G_x$ を提案する。図2(b)に $G_x(A)=[1*0*]$ , $G_x(B)=[**01]$ の例を示す。疑似許容関数集合は許容関数以外の関数を含む場合もあるが,CSPFよりも大きい許容関数集合を表現することができ、このため従来法よりも多くの回路変形候補を発見することができる。

疑似許容関数集合はCPSFより多くの関数を表現できるが、許容関数以外の関数も含む。BDDを用いて疑似許容関数を表現し、許容関数であるかどうかはBDDの等価性の判定を行うことによって容易に検査できる。

#### 3.3 疑似許容関数集合を用いた回路変形

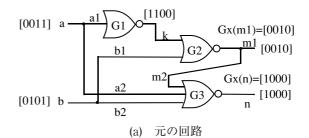

図2に疑似許容関数集合を用いた回路変形例を示す。 図2で $G_x(m_2)=[0***]$ ,  $G_x(a_2)=[0***]$ ,  $G_x(b_2)=[01**]$ . これより、 $m_2$ と $a_2$ のいずれかが削除候補となる。

(b) a2削除 (Φ=1.56)

(c) m2削除 (Φ=1.62)

図2 回路変換の例

次の章で述べる方法で、削除後の候補回路、図1(b)と図1(c)の $\Phi$ の値を計算し、その値がより多く減少する方を選択すると、図2(b)が得られる。

## 4. 疑似許容関数集合を用いた消費電力削減法

トランスダクション法とは、許容関数の概念を用いて回路の出力関数が変化しないように回路を変形する手法である。提案した疑似許容関数 $G_x$ を用いて、式(2)で定義した評価関数 $\Phi$ が小さくなるように回路を変形することで消費電力を削減する。以下に、アルゴリズムを提案する。

#### アルゴリズム

**Step1**: Φが減少しなくなるまで、出力側から順に全ゲートvに対して、**Step2**~**Step3**を繰返し実行する.

## Step2: 結線追加手続き

- **2.1** vの疑似許容関数集合 $G_x$ を求める.

- **2.2** vに接続可能なゲートのうち、最も $\Phi$ が減少するものをファンイン制限内で接続する.

- **2.3** 各ゲート出力を最計算し、回路出力が変化していないか調べ、変化していたら元に戻す.

- 2.4 2.1~2.3を接続可能結線が無くなるか,入力結線 が最大ファンイン数になるまで繰り返す.

## Step3:結線削除手続き

- **3.1** vの入力結線の疑似許容関数集合 $G_x$ を求める.

- 3.2 削除可能な入力結線のうち、最も Φ が減少する

結線を削除する.

- **3.3** 各ゲート出力を最計算し、回路出力が変化していないか調べ、変化していたら元に戻す.

- **3.4** 2.1~2.3を削除可能結線が無くなるまで繰り返す.

#### 5. 実験結果

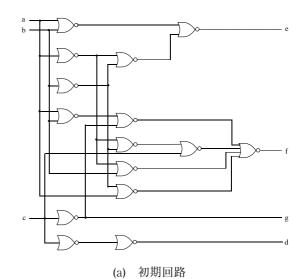

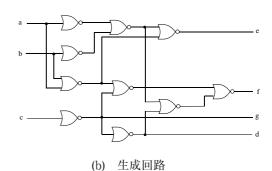

提案法の有効性を評価するため、Sun Ultra 60 (360 MHz, 512 Mbytes)上でC言語を用いて、提案法のプログラムを作成した。プログラム作成に当たり、論理関数および疑似許容関数の表現にBDDを用いた。実験ではMCNCベンチマーク回路を使用し、SIS[7]を用いて、最大ファンイン数4のNAND/NORゲートにマッピングした回路を初期回路として使用した。

消費電力の削減率 $\Phi$ は、初期回路の消費電力を $\Phi_1$ 、生成された回路の消費電力を $\Phi_2$ とするとき、 $\Phi = ((\Phi_1 - \Phi_2)/\Phi_1) \times 100$  [%] で計算する。ゲート数、結線数の削減率についても同様に算出する。

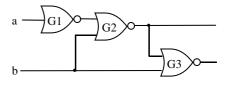

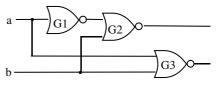

図3にベンチマーク回路b1に提案法を適用した結果を示す. 図3(a)は初期回路, 図3(b)は生成回路を示す. この場合の消費電力, ゲート数, 結線数の削減率はそれぞれ, 33.04%, 33.33%, 40.74%であった.

表1に提案手法と従来手法([3])のゲート数、結線数、 $\Phi$ の各削減率の比較結果を示す。表1には初期回路のゲート数が100以上の回路の実験結果を示した。表1からベンチマーク回路vdaの場合、提案法では消費電力の削減率 $\Phi$ が34.13%であり、従来法より18%改善された。また、b9の場合は、 $\Phi$ は10%改善された。表1の19回路中14回路において従来法より $\Phi$ の削減率が改善したが、5回路に対しては改善されなかった。

## 6. まとめ

本論文では疑似許容関数集合を用いたトランスダクション法によりCMOS回路の消費電力を削減する手法を提案し、MCNCベンチマーク回路に適用し提案法の有効性を評価した。その結果、19回路中14回路で提案法により消費電力の削減率が改善できることを示した。しかし、4個の回路に対しては改善されなかった。今後は回路変形の過程で削除すべきゲートや結線の優先順序を考慮した手法について検討する必要がある。

謝辞 提案法のプログラムの作成に御協力頂いた田中浩明君(現在,大阪大学大学院在学中)に深謝致します.

図3 b1 に対する消費電力の削減

| 回路名      | 文献 [3] (単位 [%] ) |       |       | 提案法 (単位 [%]) |       |       |

|----------|------------------|-------|-------|--------------|-------|-------|

|          | ゲート数             | 結線数   | Φ     | ゲート数         | 結線数   | Φ     |

| 9symml   | 16.00            | -2.75 | 21.14 | 15.06        | -2.75 | 20.12 |

| C432     | 24.38            | 30.38 | 30.57 | 36.63        | 28.74 | 30.08 |

| alu2     | 46.76            | 33.20 | 42.92 | 39.94        | 26.15 | 42.55 |

| apex7    | 21.45            | 18.18 | 21.67 | 19.74        | 12.82 | 20.76 |

| b9       | 12.34            | 12.82 | 18.49 | 21.74        | 16.53 | 28.46 |

| c8       | 22.28            | 25.29 | 25.83 | 22.89        | 23.50 | 26.45 |

| cht      | 13.98            | 17.70 | 17.29 | 15.95        | 12.87 | 21.21 |

| count    | 11.73            | 3.32  | 9.39  | 15.38        | 7.35  | 17.49 |

| example2 | 12.40            | 11.74 | 23.92 | 13.84        | 8.06  | 31.12 |

| f51m     | 57.82            | 54.01 | 57.46 | 45.59        | 24.55 | 49.69 |

| frgl     | 27.01            | 16.30 | 37.74 | 26.61        | 4.33  | 39.68 |

| lal      | 23.78            | 35.19 | 36.36 | 31.36        | 34.19 | 38.21 |

| mux      | 45.13            | 39.89 | 50.75 | 40.22        | 24.16 | 51.68 |

| pcler8   | 18.64            | 8.64  | 23.63 | 7.87         | 0.62  | 29.25 |

| sct      | 26.55            | 39.55 | 37.99 | 37.50        | 40.54 | 47.79 |

| term1    | 60.71            | 64.57 | 72.41 | 65.93        | 60.17 | 74.02 |

| ttt2     | 27.71            | 30.96 | 36.13 | 27.45        | 30.13 | 42.98 |

| unreg    | 0.00             | 0.00  | 0.00  | 0.00         | -9.78 | 2.23  |

| vda      | 12.58            | 15.69 | 16.34 | 29.13        | 29.36 | 34.13 |

表1 実験結果

## 参考文献

- [1] Qi Wang and Sarma B. K. Vrudhula, "Multi-level logic optimization for low power using local logic transformation", Proc. ICCAD '96, pp.270-277, 1996.

- [2] H. Ueda and K. Kinoshita, "Low power design and its testability", Proc. 4th Asian Test Symposium, pp.361-366, Nov. 1995.

- [3] 古賀一博,澤田直,安浦寛人,"トランスダクション法 を利用した組み合わせ回路の消費電力設計について", 情報処理学会DAシンポジウム論文集,pp.105-110,1997.

- [4] S. Muroga, Y. Kambayashi, H. C. Lai and N. Culliney, "The transduction method design of logic networks based on permissible functions", IEEE Trans. Computers, vol.38, pp.1404-1424, 1989.

- [5] 田中克典,熊沢雅之,幸田武範,"拡張許容関数集合を用いた回路変形",情報処理学会DAシンポジウム論文集,pp.263-268,1998.

- [6] 世古忠, "SSPFを用いたCMOS回路の消費電力の削減法" 奈良高専 研究紀要第40号, pp.65-68, 2005.

- [7] E. M. Sentovich, et al., "SIS: A System for Sequential Circuit Synthesis", Memorandom No. UCB/ERL M92/41, University of California, 1992.