# 不均一ビット幅データパスに対するテスト容易化設計法

山口 賢一·原田 和幸\*

A Design-for-Testability method for RTL datapath with various bit width

Ken'ichi Yamaguchi and Kazuyuki Harada\*

近年大規模論理回路のテスト生成を容易にするため様々なテスト容易化設計法が提案されている。従来のテスト容易化設計手法では、均一なビット幅を持つデータパスを対象としていた。そこで本稿で提案する手法は、その対象範囲を従来のデータパスから不均一なビット幅を持つデータパスへと拡張し、更に外部入出力端子数の抑制を目指す。

#### 1. 序論

近年の情報技術の普及に伴い、ディジタルシステムの信頼性の向上は重要な課題となりつつある。集積回路に関しては、出荷テストを行うことによってその信頼性を確保している。しかしながら出荷テストは、今日の集積化技術の向上により、次第に困難となりつつある。そこで今日ではテスト容易化設計(以下、DFT: Design For Testability)と呼ばれる、テスト時の負担を抑制する設計手法が考案されている。

現在主流なDFTであるスキャン設計は、回路規模の大規模化に伴い、テストパターンの計算時間が増大するという問題点がある。スキャン設計の問題点を解消するため、DFHT (Design For Hierarchical Testability) 」と呼ばれるDFT 手法が提案された。DFHT は回路の構成要素である各モジュールに対し、そのモジュールを外部からテストするためのデータの転送経路を構築する。DFHTではDFTのためのアルゴリズムは複雑になるが、一定の回路面積を持つモジュール単位でテストパターンを求めればよいので、回路規模が増大してもテストパターンの計算時間は増大しないという利点がある。しかしながらDFHT は回路の持つビット幅に対する制約が厳しく、全信号線が同じビット幅を持つ回路を仮定している。従ってDFHT は不均一なビット幅を持つ回路に直接適用することはできない。

不均一なビット幅を持つ回路に対応したDFT 手法として文献<sup>2)</sup> や文献<sup>3)</sup> のような手法が提案されているが、前者はDFHTではなくスキャン設計に基づく手法であるため、テストパターンの計算時間が増大する。また後者はDFHT

に基づく手法であるがアルゴリズムが論文で明確に定式 化されていないため、手法の有効性を調査することがで きない、また入出力端子数が大幅に増大するという問題 点がある.

以上のように、不均一なビット幅を持つ回路を対象としたDFTには未だ有効な手法が存在しないというのが実情である。そこで本稿では、従来のDFHTにおけるビット幅の制約をなくし、更にDFTによって増加する外部入出力の抑制を試みる。

## 2. DFHT 手法

Design For Hierarchical Testability (以下, DFHT) 1) は、Ghosh らによって提案されたDFT である. 現在では DFHT を改良した手法として文献4)、文献5) に挙げる手法 などが提案されている. DFHT はレジスタ転送レベル (以下, RTL: Register Transfer Level) の段階における回 路記述を対象としている. RTL はシステムの設計抽象度 の1 つであり、動作レベルよりも下位で、ゲートレベルよ りも上位の抽象度に位置する. RTL の詳細は3.1 節で説明 する. DFHT ではまず、RTL 内に存在する各モジュール (回路要素) に外部入力からテストパターンを入力し、テ ストパターンに対する応答を外部出力で観測できるよう なデータの転送経路(以下,経路)を構築する.次に各 モジュールのテストパターンをテスト生成アルゴリズム によって求め、構築しておいた経路を利用してテストパ ターンの入力,及び応答の観測を実現する.RTL におけ る各モジュールは一定の面積を持つ小規模な回路である ため、テストパターンは容易に求めることができる.

#### 3. 定義

#### 3.1 レジスタ転送レベル回路(RTL)

DFHTの対象となるRTLは、データに対して演算を行うデータパス部と、そのデータパス部を制御するコントローラ部から成る。本節では本稿で提案する手法が対象とする不均一ビット幅データパス(以下、VDP: Variouse bit width Data path)を数学的に定義する。

データパスは回路要素と呼ばれる機能単位のモジュールを信号線を用いて接続することによって構成する. RTLの回路要素は大きく分けて、外部入出力、組合せ回路要素、順序回路要素、頂点の4種類がある。各回路要素は種類ごとに固有の数の入出力端子を持つ。また信号線は、ある回路要素の出力端子と、ある回路要素の入力端子を接続する。データパス内部の全回路要素の集合をVとする。このときV=Vpio  $\cup$  VcmD0 $\cup$  VseqD0 $\cup$  Vpoint D0 $\cup$  D0 D0 $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$  D0  $\cup$   $\cup$  D0  $\cup$   $\cup$  D0  $\cup$   $\cup$  D0  $\cup$

#### 3.2 外部入出力集合Vpio

外部入出力には外部入力と外部出力の2種類がある.外部入力は1個の出力端子のみを持つ.外部出力は1個の入力端子のみを持つ.

ここで,

- Vpi:外部入力の集合.

- *Vpo*:外部出力の集合.

としたとき,  $Vpio = Vpi \cup Vpo$  である.

## 3.3 組合せ回路要素集合Vcmb

組合せ回路要素には、マルチプレクサ(以下、MUX:MUltipleXer)、演算器の2 種類がある。 組合せ回路要素はいずれも2 個の入力端子と1 個の出力端子を持つ。ここで、

- Vmux: MUX の集合.

- Vn\_mux:通常のMUXの集合.

- Vtdic\_mux: TDIC 用のMUX の集合.

- Vtdro mux: TDRO 用のMUX の集合.

- Vop:演算器の集合.

とする.  $Vtdic\_mux$  と $Vtdro\_mux$  は後節にて説明する. このとき $Vmux = Vn\_mux$   $\cup$   $Vtdic\_mux$   $\cup$   $Vtdro\_mux$  であり,またVcmb = Vmux  $\cup$  Vop である.

#### 3.4 順序回路要素集合Vseq

順序回路要素には、ホールド機能無しレジスタとホールド機能付きレジスタの2種類がある。順序回路要素はいずれも1個の入力端子と1個の出力端子を持つ。ホールド機能無しレジスタに入力されたデータは、1クロックだけ保持し、次のクロックで出力する。ホールド機能付きレ

ジスタはホールド機能により、以前のデータを保持する ことができる.ここで、

● Vn\_reg:ホールド機能無しレジスタの集合.

•  $Vh\_reg$ : ホールド機能付きレジスタの集合. としたとき,  $Vseq=Vn\_reg \cup Vh\_reg$ である.

## 3.5 頂点集合Vpoint

頂点には、セパレート点、バインド点、ファンアウト点、ターミナル点がある。セパレート点は1個の入力端子と2個の出力端子を持ち、入力をビット単位で2つの出力に分割する。従って入力ビット幅は、2つの出力ビット幅の和となる。バインド点は2個の入力端子と1個の出力端子を持ち、2つの入力をビット単位で出力に統合する。従って出力ビット幅は、2つの入力ビット幅の和となる。ファンアウト点は1個の入力端子と2個の出力端子を持ち、信号線の分岐を意味する。すなわち、入力と同じデータを2つの出力端子に出力する。従って入力ビット幅とそれぞれの出力ビット幅は同じ値となる。ターミナル点は1個の入力端子と0個の出力端子を持ち、信号線の終端を意味する。ここで、

● Vseparate: セパレート点の集合

● Vbind:バインド点の集合

● Vfanout:ファンアウト点の集合

● Vterminal:ターミナル点の集合

としたとき、 $Vpoint=Vseparate \cup Vbind \cup Vfanout \cup Vterminal$ である.

## 4. ビット幅圧縮・ビット幅拡張

本節では提案するテスト容易化設計(DFT)で使用する, ビット幅を圧縮・拡張するアイデアについて説明する.

## 4.1 時分割応答観測(先行手法)

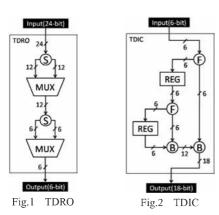

時分割応答観測(以下、TDRO: Time Division Response Observation)のは、外部出力よりも大きなビット幅を持つ回路要素の出力端子からの応答データを、外部出力で時分割に観測することを目的としたDFT アイデアである。TDRO は文献ので提案されたビット幅調整回路(bit match circuit)に基礎を置いている。TDRO の例を次ページFig. 1 に示す。Fig. 1 では入力をセパレート点(S と書かれた円)を用いて分割し、それぞれ2 段に挿入したMUX(MUX と書かれた台形)に入力している。テスト時にはMUX の入力を適宜選択することにより、データを時分割に観測することができる。また本稿ではTDROを実現する際に挿入されるセパレート点、MUX をまとめてTDRO-Unit と呼ぶ。

#### 4.2 時分割入力制御(提案手法)

提案手法である時分割入力制御(以下、TDIC:Time Division Input Control)は、TDRO の時分割でビット幅調整を行うという考え方を入力に応用したDFT アイデアである。TDIC を用いることにより、外部入力よりも大きなビット幅を持つ回路要素の入力端子にテストパターンを入力することができる。TDIC の例をFig. 2に示す。Fig. 2では入力を2つのファンアウト点(Fと書かれた円)で分岐し、2つのホールド機能無しレジスタ(REGと書かれた長方形)に分割して保持し、最後にそれらをバインド点(Bと書かれた円)により統合する。テスト時にはテストパターンを上位6ビットから6ビットずつ順番に1クロックごとに入力すれば、元のテストパターンを再現できる。TDIC-Unitと同様に、TDICを実現するために挿入されるTDIC、ファンアウト点、バインド点をまとめてTDIC-Unitと呼ぶ。

## 5. データパスの定義の拡張

本節では提案するDFT アルゴリズムを記述するため、 データパスの定義を拡張する.

#### 5.1 回路要素から入出力端子への写像

VDP 内の全回路要素の入力端子全体の集合をIN、出力端子全体の集合をOUTとする。このとき回路要素ごとの入出力数に応じて、VとIN、もしくはVとOUTとの対応を写像として定義する。

#### 5.1.1 1入力回路要素

VDP内の1入力回路要素を $V_1$ \_input =  $V_{po} \cup V_{seq} \cup V_{separate} \cup V_{fanout} \cup V_{terminal}$ とする. このとき、 $v \in V_1$ \_inputとその入力端子 $a \in IN$ との対応を、写像Inputとして下式のように定義する.

$Input = \{(v,a) \in V_1 \ input \times IN | a は v の 入力端子\}$

#### 5.1.2 1出力回路要素

VDP内の1出力回路要素を $V_1\_output = Vpi \cup Vcmb \cup Vseq \cup$

*Vbind*とする. このとき,  $v \in V_1$ \_outputとその出力端子 $c \in OUT$ との対応を, 写像Outputとして下式のように定義する.  $Output = \{(v,c) \in V_1 \ output \times OUT | c$ はvの出力端子 $\}$

## 5.1.3 2入力回路要素

VDP内の2入力回路要素を $V2\_input=Vcmb$   $\cup$  Vbind とする. また、 $v \in V2\_input$  の2つの入力端子をそれぞれa、b  $(\in IN)$  とする. このとき、v とa,b のペア (a,b) との対応を、写像InputPair として下式のように定義する.

$InputPair = \{ (v, (a,b)) | a,b は v の入力端子かつ a \neq b \}$

## 5.1.4 2出力回路要素

VDP内の2出力回路要素を $V_{2-output} = V_{fanout} \cup V_{separate}$  とする。また、 $v \in V_{2-output}$  の2つの出力端子をそれぞれc, d ( $\in OUT$ ) とする。このとき、v とc,d のペア (c,d) との対応を、写像OutputPair として下式のように定義する。

$OutputPair = \{ (v, (c,d)) | c, d は v の出力端子かつ c \neq d \}$

## 5.2 入出力端子から回路要素への写像

入出力端子と回路要素の対応を写像として定義する。 入力端子と出力端子の集合 $IN \cup OUT$  からその回路要素Vへの写像Module を下式のように定義する。

$Module = \{ (x, v) | x は v の入力端子または v の出力端子 \}$

## 5.3 信号線

回路要素間を接続する信号線は、出力端子 $out \in OUT$  と入力端子 $in \in IN$  を接続する。ここでは信号線を表現する写像としてNext とPrev を定める。VDP 内の入力端子ex  $\in IN$ ,出力端子ex ext ext

$Next = \{ (y, x) | y からx への信号線がVDP に存在する \}$  $Prev = \{ (y, x) | y からx への信号線がVDP に存在する \}$

#### 5.4 ビット幅

VDP 内の信号線はそれぞれ固有のビット幅を持つ. ここでは入出力端子 $IN \cup OUT$  からそのビット幅への写像u を定義する. VDP 内の入出力端子をx ( $\in IN \cup OUT$ ), その入出力端子が接続している信号線のビット幅をk ( $\in N$ ) とする. このときx とk の対応を意味する写像u を下式のように定義する.

$u = \{ (x, k) \in (IN \cup OUT) \mid x \ \text{tik} \ \text{のビット幅を持つ} \}$

## 6. 単一制御可検査不均一ビット幅データパス

本稿でDFT の対象とするのはデータパスである. コン

トローラではなくデータパスを対象とするのは、一般的にコントローラよりもデータパスの方が面積が大きいため、DFT の影響がより表面化するからである。データパスのテストの容易性を評価するために、そのデータパスが満たすべき様々な条件が定義されている。単一制御可検査性<sup>(1)</sup> は、テスト容易なデータパスが満たすべき条件である。

しかしながら単一制御可検査性はビット幅を考慮しないデータパスに対して定義されたものであるため、不均一ビット幅データパス(VDP)のテスト容易性を評価する際には定義を拡張する必要がある。そこで、単一制御可検査データパスを拡張し、ビット幅を考慮した単一制御可検査性を新たに定義する。またそれを満たすVDPを単一制御可検査不均一ビット幅データパス(以下、SC VDP)とする。

データパスがSC VDP であるためには、データパスの各組合せ回路要素 $M \in V$  が以下の3 条件を満たす必要がある

- 外部入力からM の両入力端子の各ビットに,任意の 値を伝搬可能

- *M* の出力端子の各ビットから外部出力に任意の値を 伝搬可能

- 上記2 条件の達成にTDIC, TDRO の使用を許可 次節以降では、与えられたデータパスをSC VDP に変換 するための提案アルゴリズムを説明する.

## 7. DFT の前処理

ここでは前処理として、与えられたVDP に対し、TDIC-Unit 及びTDRO-Unit の付加を行う.

#### 7.1 TDIC-Unit の付加

VDP の全外部入力 $pi \in VPI$  のビット幅の和をSPI とする. すなわち,

$$S_{PI} = \sum_{pi \in V_{PI}} u(output(pi))$$

また、各組合せ回路要素 $v \in Vcmb$  の入力端子a, b (ここで (a, b) = InputPair (v)) のビット幅の和u (a) + u (b) のうち、データパス中最大の値を $M_{IN}$  とする。すなわち、

$$M_{IN} = max(u(a) + u(b))$$

もし対象としているデータパスがSPI < MIN ならば、ある回路要素の入力端子にテストパターンを供給するための外部入力が不足しているため、データパスは $SC\ VDP$  ではない、従って、TDIC-Unit を付加して外部入力のビッ

ト幅を拡張する. なお $SPI \ge M_{IN}$  のときは、TDIC-Unit の付加は必要ない.

付加するTDIC-Unit は $S_{PI}$ の入力ビット幅と $M_{IN}$ の出力ビット幅を持つ.

#### 7.2 TDRO-Unit の付加

TDIC-Unit と同様にして、TDRO-Unit も予め付加しておく、データパスの全外部出力 $po \in V_{PO}$  のビット幅の和 $S_{PO}$  は以下のようになる、

$$S_{PO} = \sum_{po \in V_{PO}} u(input(po))$$

各組合せ回路要素 $v \in Vcmb$  の出力端子c = Output (v) のビット幅のうち、データパス中最大の値をMOUT とする、すなわち、

$$M_{OUT} = max(u(c))$$

もし対象としているデータパスがSPO < MOUT ならば、ある回路要素の出力端子から応答を観測するための外部出力が不足しているため、データパスはSC VDP ではない。従って、出力端子の信号をTDRO-Unit を用いて圧縮する必要がある。なお、 $SPO \ge MOUT$  のときは、TDRO-Unit の付加は必要ない。

付加するTDRO-Unit は $M_{OUT}$ の入力ビット幅と $S_{PO}$ の出力ビット幅を持つ.

#### 8. テストパターン供給の実現

VDP をSC VDP に変換するためには、各組合せ回路要素M にテストパターンが供給できる必要がある。M へのテストパターン供給は、M の入力端子とTDIC-Unit の出力をMUX を用いて接続することによって実現できる。MUX を介して入力する理由は、データパスの通常動作時の挙動に影響を及ぼさないためである。このMUX をTDIC MUX と呼ぶ。

ところで付加するTDIC MUX は、既に付加されている TDIC MUX と共有することができる。すなわちM のテストパターン供給の実現のために挿入されるTDIC MUX を可能な限り共有することで、DFT の面積増加を抑制することができる。そこで、M の入力にTDIC MUX を挿入する際に、TDIC MUX の探索を行う。

#### 8.1 TDIC MUX 探索アルゴリズム

TDIC MUX は,M の入力端子を始点とし,信号の流れと逆の方向(入力端子から出力端子)に探索する.ここでM の2 つの入力端子をそれぞれa, b ((a, b) = InputPair (M))とする.また,u (a)  $\geq u$  (b) である.探索はまずa を始点に探索し,その後b を始点に探索する.

#### 8.1.1 入力端子a を始点とした探索

a と信号線を介した回路要素をv とする. すなわちv = Module (Prev (a)) である. v の種類によって以下のような操作を施す.

- v ∈ Vpi ∪ Vtdic\_mux の場合: v がPI, もしくはTDIC MUX の場合は、M のテストパターン供給用に新たにTDIC MUX を付加する必要がない。従ってTDIC MUX を付加せずに探索を終了する。

- $v \in Vn\_mux$  の場合: v が通常のMUX の場合は、その MUX から探索を再開する. しかしb が同じ経路を使用してしまうと、SC VDP を満たさなくなる. そこで a が使用した経路を区別するために、ここでv にチェックを付けておく. その後 (x,y) = InputPair(v) としたとき、max(u(x),u(y)) のビット幅を持つ 入力端子を新たにa とする. そしてa と信号線を介して接続する回路要素を新たにv = Module(Prev(a)) として探索を続行する.

- $v \in Vop \cup Vbind$  の場合: v が演算器, もしくはバインド点の場合は, TDIC MUX を付加して探索終了となる. v の出力端子Output (v) = Prev (a) とその時点でのa の間に, u (a) のビット幅を持つTDIC MUX を挿入する.

- $v \in Vseparate \cup Vseq$  の場合: v がセパレート点,もしくは順序回路要素の場合は, Input (v) を新たにaとし、Module (Prev (a)) を新たにv として探索を続行する.

- $v \in V fanout$  の場合: v がファンアウト点の場合は、MUX と同様にv にチェックをつけた後、Input (v) を新たにa とし、Module (Prev (a)) を新たにv として探索を再開する.

## 8.1.2 入力端子b を始点とした探索

入力端子bの探索はvが通常のMUXの場合とファンアウト点の場合以外は、入力端子aの探索と同様にして行う.

- $v \in Vn\_mux$  の場合: v が通常のMUX の場合は、v に チェックが付いていればTDIC MUX を付加して探索 を終了する. チェックが付いていなければ、a の場合と同様に探索を再開する.

- $v \in V fanout$  の場合: v がファンアウト点の場合は, v にチェックが付いていればTDIC MUX を付加して探索を終了する. 付いていなければa の場合と同様に探索を再開する.

#### 9. 応答観測の実現

前節でM にテストパターンを供給するための経路を実現した。しかしVDP をSC VDP に変換するためには更に、M の応答観測を実現する必要がある。提案手法では、応答観測を実現するために、M の出力端子のビット幅をTDRO-Unit で調整する。TDRO-Unit の入力とM の出力端子を結ぶMUX をTDRO MUX と呼ぶ。TDRO MUX の付加の場合もTDIC MUX のときと同様に、面積抑制のための探索を行う。

## 9.1 TDRO MUX 探索アルゴリズム

TDRO MUX は、M の出力端子を始点とし、信号の流れと同じ方向に探索する。M の出力端子をc = Output (M) とする.

#### 9.1.1 出力端子 からの探索

c と信号線を介して接続している回路要素をv = Module (Next (c)) とする.

- v ∈ Vpo ∪ Vtdro\_mux の場合: v がPO, もしくは TDRO MUX の場合は、M の応答観測用に新たに TDRO MUX を付加する必要がない。従ってTDRO MUX を付加せずに探索を終了する。

- v ∈ Vn\_mux ∪ Vtdic\_mux ∪ Vseq ∪ Vbind の場合: v が通常のMUX, TDIC MUX, 順序回路, バインド 点の場合は, Output (v) を新たにc とし, Module (Next (c)) を新たにv として探索を再開する.

- $v \in Vop$  の場合: v が演算器の場合は、TDRO MUX を付加して探索終了となる。その時点でのc とNext (c) の間にu (c) のビット幅を持つTDRO MUX を挿入する。

- v ∈ Vseparate ∪ Vterminal の場合: v がセパレート点 かターミナル点の場合は、TDRO MUX を付加して 探索終了となる。その時点でのc とNext (c) の間にu (c) のビット幅を持つTDRO MUX を挿入する。

- $v \in V fanout$ の場合:ファンアウトの場合は、出力端子 のペアを (x,y) = OutputPair(v) としたとき、x かy のどちらかを任意に選択して新たにcとし、Module(Next(c)) を新たにvとして探索を続行する.

## 10. 提案するDFT 手法のまとめ

8. 節と9. 節の操作を経ることにより、各組合せ回路

要素 $M \in V$  はTDIC-Unit を介してテストパターンの供給が可能となり、かつTDRO-Unit を介して応答観測が実現できる。従って、以上でVDP のSC VDP への変換は達成できた。

SC VDP に変換したデータパスは、各 $M \in V$  に対するテストパターンが存在すれば信頼性の高いテストを実現できる。そこで次節では提案するDFT 手法を実際のVDP に適用して故障シミュレーションを行うことにより、その有効性と欠点を調査する。

## 11. 提案手法の適用例

提案手法の有効性を評価するために、不均一なビット幅を持つベンチマークデータパスに対して提案手法を適用した、提案手法を適用したデータパスはLWF(3rd Lattice Wave Filter)とWRTである.

いずれのデータパスもVHDLで記述し、Synopsys 社の論理合成ツールDesign Analyzer を用いて回路面積を算出した。ここで、DFT 適用前から適用後に増えた面積の比率を面積増加率とする。また、Synopsys 社の故障シミュレータTetra Max を用いて、データパス内の各回路要素の全単一縮退故障を検出可能なテストパターン数を算出した。そして得られたテストパターン数とTDIC 及びTDRO に要する時間を掛け合わせた結果をテスト実行時間とする。

LWF, WRT に対する提案手法の適用前と適用後の面積, 面積増加率,外部入出力数,テスト実行時間をTable 1, Table 2 に示す.尚,適用前のテスト実行時間は,TDIC 及びTDRO を使用しないときの各回路要素のテストパターン数の和を示している.

Table 1 提案手法の適用前と適用後(LWF, WRT)

|     | 回路面積 |      | 面積 外部入出力数 |     | 出力数 |

|-----|------|------|-----------|-----|-----|

|     | 適用前  | 適用後  | 増加率       | 適用前 | 適用後 |

| LWF | 1121 | 1373 | 22.5%     | 44  | 44  |

| WRT | 580  | 696  | 20.0%     | 18  | 18  |

Table 1 によると、DFT 適用によるLWF とWRT の外部 入出力数の増加は0 である.これは外部入出力の付加が困 難な状況における、提案手法の有効性を示唆している.

Table 2 提案手法の適用前と適用後(LWF, WRT)

|     | テスト実行時間 |     | テスト実行時間 |  |

|-----|---------|-----|---------|--|

|     | 適用前     | 適用後 | 増加率     |  |

| LWF | 108     | 292 | 170%    |  |

| WRT | 76      | 180 | 237%    |  |

しかしながらテスト実行時間はいずれも2倍~3倍に増加している。これはTDICとTDROの時分割回数に依存し

ている。従って提案手法は、LWF やWRT のように外部入出力のビット幅の和が回路要素のビット幅よりも極端に小さいデータパスに適用する際には、テスト実行時間が大幅に増大するという欠点がある。改善案としては、各回路要素間のテストパターンの共通部分を利用した連続クロックでのテストなどが考えられる。

#### 12. 結論

本稿では不均一なビット幅を持つデータパスに対する テスト容易化設計 (DFT) 手法を提案した.

提案したDFT 手法では外部入出力の付加を抑制するため, TDRO 及びTDIC を用いた. どちらも外部入出力と回路要素のビット幅の差を埋めるために使用する.

提案するテスト容易化設計アルゴリズムでは、付加するマルチプレクサ(MUX)を抑制するために、MUXの探索を行う.新たにMUXを付加する場所へとデータが到達可能な範囲でMUXが既に付加されていたならば、新たにMUXを付加する必要はないからである.

提案手法をベンチマークデータパスに適用したところ, DFTによる外部入出力の増加の抑制を達成した.

## 参考文献

- 1) I.Ghosh, A.Raghunath and N.K.Jha: "Design for hierarchical testability of RTL circuits obtained by behavioral synthesis," IEEE ICCD' 95, pp.173-179

- 2)Y.Murata, S.Ohtake and H.Fujiwara: "A method of DFT for data paths using bit-match function," 情報処理学会研究報告. SLDM, Vol.2004, No.122(20041201), pp.137-142

- 3) H.Date, T.Hosokawa, M.Miyazaki, and M.Muraoka: "A Nonscan DFT Method for RTL Data Path Circuits with Various Bit Width," IEEE Proceedings of The 3rd Workshop on RTL and High Level Testing, pp.32-37

- 4) T.Masuzawa, M.Idutsu, H.Wada and H.Fujiwara: "Single control testability of RTL data paths for BIST,"

Ninth Asian Test Symposium (ATS' 00), p.210

- 5) K.Yamaguchi, M.Inoue and H.Fujiwara: "Hierarchical BIST: Test-per-clock BIST with low overhead," Digest of Papers, IEEE 3rd Workshop on WRTLT' 02, pp.42-47

- 6) 青山瑠美, 山口賢一: "不均一bit 幅データパスに対す る組込み自己テスト法," FIT2005 (情報科学技術フォ ーラム)

- 7) M.Nourani and C.A.Papachristou: "Structural Fault Testing of Embedded Cores Using Pipelining," JETTA vol.15, pp.129-144